Integrated Circuit (IC) technology is continuously scaling down to smaller transistor sizes, allowing to keep up with the increasing demand on computational capacity of today’s broad range of applications. As we penetrate the sub-micron era, sub-threshold leakage and global interconnect delays have become a major bottleneck for both power and performance. Three-dimensional (3D) IC stacking is an attractive path to overcome the interconnect scaling issues. By exploiting the vertical dimension, it is possible to considerably shorten the wire lengths between SoC components, hence boost the performance and achieve high integration densities. The recent progress in the fabrication of through silicon vias (TSVs) and bond pads allow to achieve dense arrays of interconnects between the vertically stacked tiers. For a memory-on-computer architecture, this provides orders of magnitude higher bandwidth than in a traditional 2D system-on-chip. Additionally, 3D stacking enables the integration of different technologies in a single heterogeneous chip.

However, the 3D IC stacking technology is still not widely used because of lack of design guidelines, test methods, tools and equipment, but also because of technical challenges. In particular, conventional heat sinks encounter major difficulties in keeping the temperature of a 3D stack within the operational range. The integration of liquid micro-cooling channels between the interconnect vias in the silicon substrate has been proven to efficiently address this 3D SoC heating problem, being able to cool the stack throughout the whole volume. A second challenge that 3D integration faces is power delivery. To supply the necessary voltage from the PCB to several layers in a 3D stack, a large fraction of the available vertical vias needs to be utilized. This can dramatically limit the inter-layer communication bandwidth and undermine the benefits of 3D integration technology.

Thermal and power management/optimization is a crucial aspect in the future of 3D stacked SoC design. Researchers in the state of the art are proposing effective design solutions and methods to efficiently benefit from the 3D integration advantages. Such efforts are needed for 3D stacking to become widespread in IC design industry.

Goal:

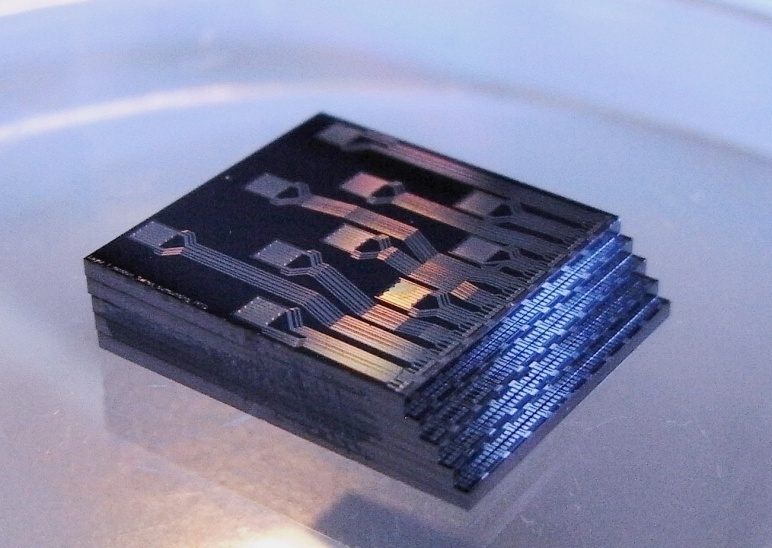

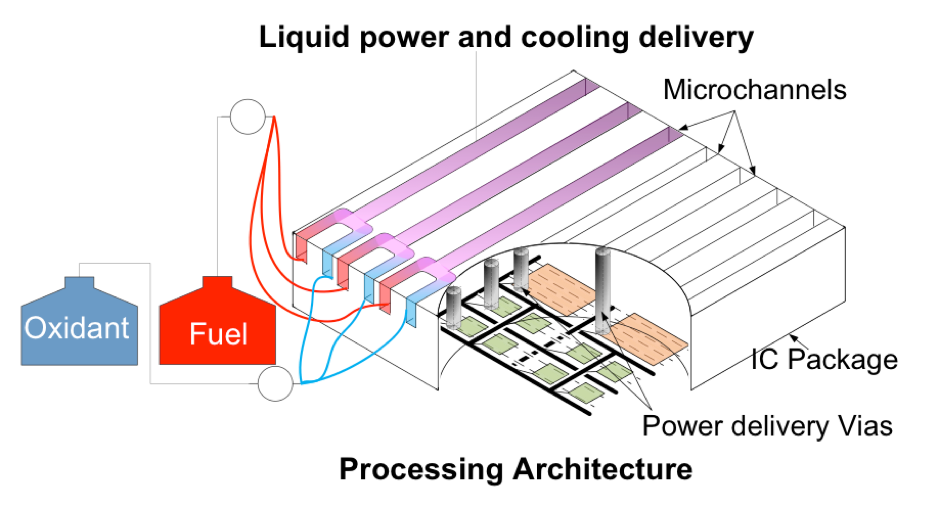

In the ESL laboratory, we aim to address two major challenges of 3D integration, namely heat removal and power delivery of vertically stacked dies. To the best of our knowledge, we are the first research group to propose a combined cooling and on-chip power generation/delivery method for 3D stacked ICs. We have developed a simulation tool, called PowerCool, to model steady-state operation of a 3D SoC with integrated flow cell arrays (FCAs) technology. The FCAs consist of several inter-tier micro-channels filled with an electrolytic solution, they are placed in the silicon substrate of each die. The FCAs provide liquid cooling to the 3D chip, at the same time electro-chemical reactions take place between the electrolytes, which generates electrical power. This power can be directly supplied to the active circuit in the same die, or delivered to nearby dies via dedicated TSVs and microbumps. A continuous flow of the electrolytic liquid ensures a steady cooling and energy supply for the stacked dies. Figure 3 shows the electrical model of a flow cell array.

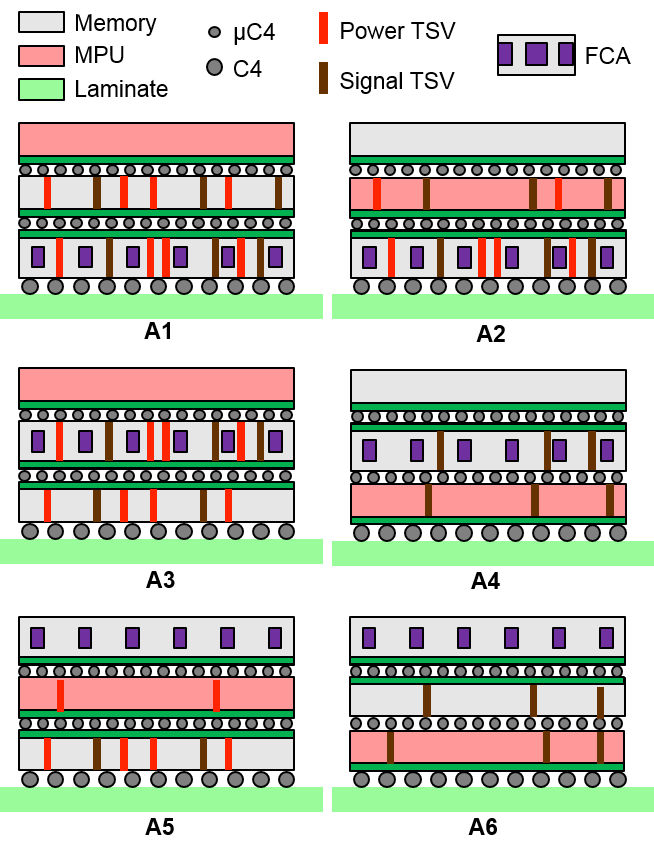

One main part of this project consists on studying, developing, testing and validating the FCA technology. We demonstrate the accuracy of the electro-chemical model by comparing its results with actual micro-scale flow cell. Another important part of the project is qualitatively analyzing the impact of FCAs on 3D SoCs and comparing its performance against conventional air-cooled 2D technology and 3D chips without micro-fluidic channels. We model different 3D stack architectures including processing units and memories. The next figure depicts different possible stack arrangements with integrated FCAs. We evaluate the heat-removal and the power generation capabilities of the FCAs for different 3D chip models using our PowerCool simulator, which combines electro-chemical and thermal simulations to output full system state for a given set of control and design parameters.

Developed software tools:

- The 3D-ICE thermal simulator

- PowerCool tool, for the simulation of Flow Cell Arrays

Videos

Related Publications

| Enabling Optimal Power Generation of Flow Cell Arrays in 3D MPSoCs with On-Chip Switched Capacitor Converters | |||||

| Najibi, Halima; Hunter, Jorge; Levisse, Alexandre Sébastien Julien; Zapater Sancho, Marina; Vasic, Miroslav; Atienza Alonso, David | |||||

| 2020 | IEEE Computer Society Annual Symposium on VLSI, Limassol, Cyprus, July 6-8, 2020 |  |  | ||

| Towards Deeply Scaled 3D MPSoCs with Integrated Flow Cell Array Technology | |||||

| Najibi, Halima; Levisse, Alexandre S�bastien Julien; Zapater Sancho, Marina; Aly, Mohamed Mostafa Sabry; Atienza Alonso, David | |||||

| 2020 | ACM Great Lakes Symposium on VLSI (GLSVLSI), Beijing, China, September, 7-9, 2020 |  |  | ||

| A Design Framework for Thermal-Aware Power Delivery Network in 3D MPSoCs with Integrated Flow Cell Arrays | |||||

| Najibi, Halima; Levisse, Alexandre S�bastien Julien; Zapater Sancho, Marina | |||||

| 2019 | ACM/IEEE International Symposium on Low Power Electronics and Design, Lausanne, Switzerland, July 29-31, 2019 |  | |||

| Design Optimization of 3D Multi-Processor System-on-Chip with Integrated Flow Cell Arrays | |||||

| Andreev, Artem; Kaplan, Fulya; Zapatero Sancho, Marina; Coskun, Ayse K.; Atienza Alonso, David | |||||

| 2018 |  |  | |||

| PowerCool: Simulation of Cooling and Powering of 3D MPSoCs with Integrated Flow Cell Arrays | |||||

| A. A. Andreev, A. Sridhar, M. M. Sabry Aly, M. Zapater and P. Ruch et al. | |||||

| 2017 | IEEE Transactions on Computers | p. 1-1 |  |  |  |

| PowerCool: Simulation of Integrated Microfluidic Power Generation in Bright Silicon MPSoCs | |||||

| A. Sridhar, M. M. Sabry, P. Ruch, D. Atienza Alonso and B. Michel | |||||

| 2014 | IEEE/ACM 2014 International Conference on Computer Aided-Design (ICCAD) |  | |||

| Integrated Microfluidic Power Generation and Cooling for Bright Silicon MPSoCs | |||||

| M. M. S. Aly, A. Sridhar, D. Atienza Alonso, P. Ruch and B. Michel | |||||

| 2014 | IEEE/ACM 2014 Design Automation and Test in Europe (DATE) Conference, Dresden, Germany | ||||