A simple, yet complete, configurable, and extendable platform base

Keywords

#riscv #energyefficiency #hardware #computerarchitectureTeam

Visit our website!

The advancement of continuous healthcare monitoring depends on the development of new and more efficient ultra-low power wearable platforms as well as new algorithms. However, the teams that develop the algorithms are usually not the same as those that design the platforms, thus, optimization opportunities are often lost in the way. Not less importantly, the availability of widespread high-performance, low-power edge-computing platforms will help to alleviate the reliance on cloud data centers and contribute to a more distributed use of energy compatible with local energy generation or harvesting.

To ensure the continuing development of new algorithms for biosignal processing, we aim to develop a prototyping environment that allows algorithm developers to assess the implications of their high-level decisions, without overwhelming them with the low-level platform details. This project is based on the open-source X-HEEP (eXtendable Heterogeneous Energy-Efficient Platform) developed at the Embedded Systems Laboratory (ESL) of the EPFL. The X-HEEP project is a fully open-source RISC-V microcontroller, and in fact, it will join the Open Hardware Group to be adopted by the open-source community at large as a reference RISC-V microcontroller.

"X-HEEP can be configured to target small and tiny platforms as well as extended with accelerators for more performance demanding applications," says Dr. Davide Schiavone, the leader of the project at ESL. "The interesting thing about X-HEEP is that we provide a simple, customizable MCU composed by an open-source, industrial-grade RISC-V CPU, common peripherals (e.g., UART, SPI, JTAG), and memories, and the users will extend it with their own accelerators in an agile way, without the need of modifying internally the MCU, but only by instantiating it in their custom design. By doing so, the user inherits an IP capable of booting an RTOS (such as freeRTOS) with the whole SW stack, including drivers and SDK, and focus only on building the special HW that makes the user's application unique."

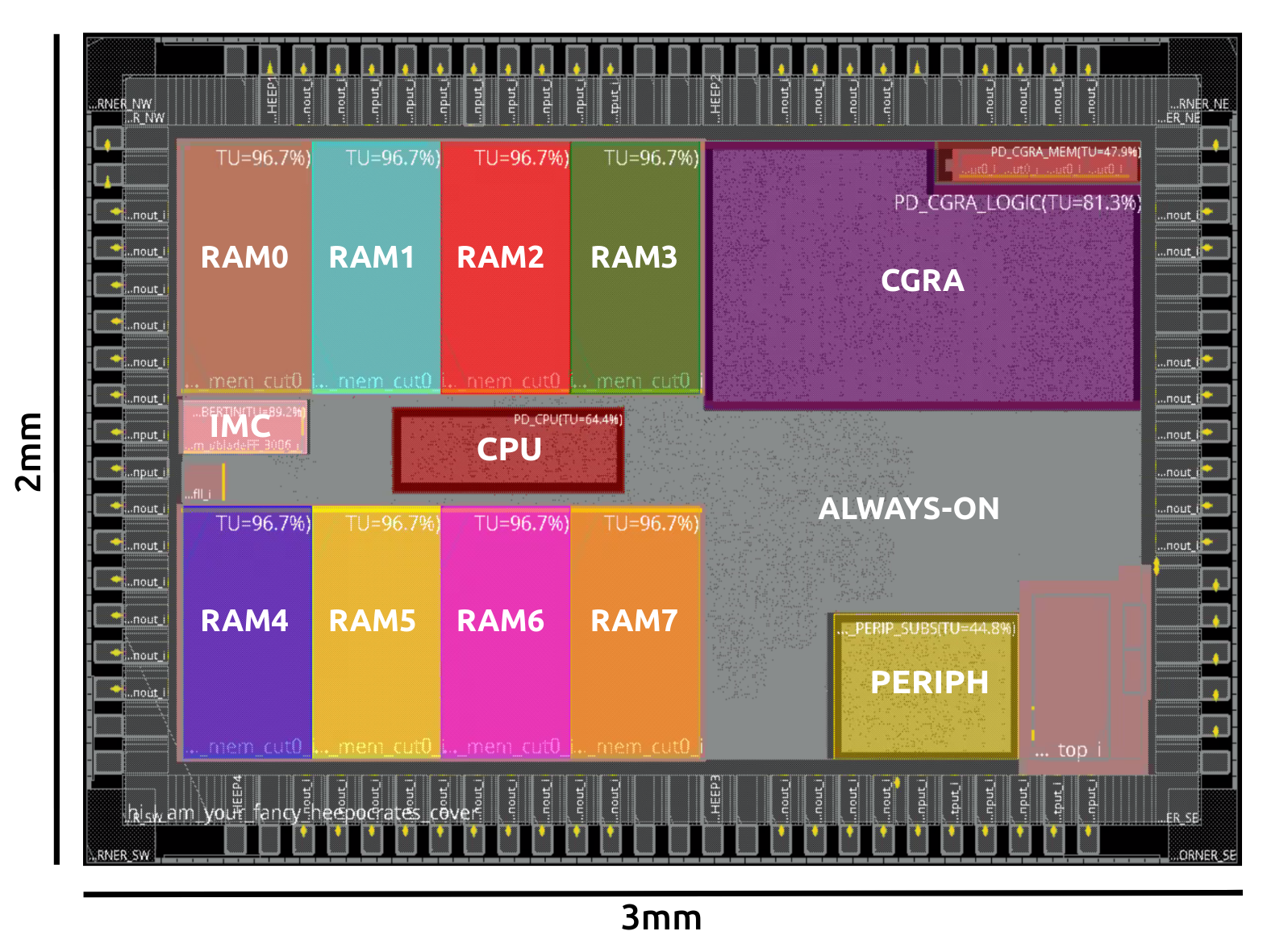

X-HEEP targets both FPGA and ASIC implementations. In fact, the support for Xilinx-based FPGAs is available open-source, while its first silicon implementation was just delivered last month. Once the chip (called HEEPocrates) is back at ESL, it will be tested and characterized in real-life settings. The measured results will be used so that programmers will be able to estimate the energy consumption of their algorithms running directly on a commonly available FPGA.

We will exploit the FPGA version of X-HEEP as baseline and extend it with additional characteristics such as virtual ADCs and time compression to enable easy prototyping and benchmarking of biomedical algorithms. We will work to ensure that the platform is as accessible as possible for a wide range of users - particularly those in other domains such as bioengineering and the mathematical development of new biomedical algorithms.

X-HEEP is open-source and free to use, download it and start using it at:

https://github.com/esl-epfl/x-heep

Do not forget to leave us a github star if you like it 🙂

The first X-Agora, 1st December 2023

HEEPocrates Test Chip layout in TSMC 65nm LP

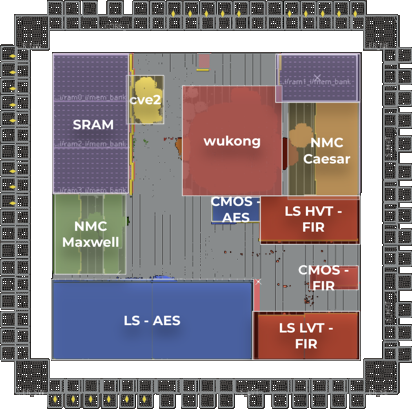

HEEPnosis Test Chip layout in GF 22nm FDX