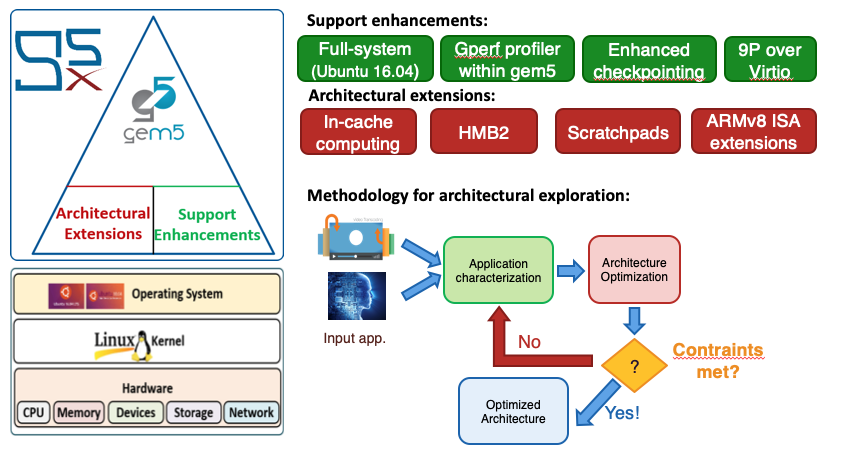

| | Project/Tool scope:gem5-X stands for a gem5-based full-system simulator with architectural eXtensions. gem5-X is a gem5-based simulator that allows architectural exploration and optimization of heterogeneous systems. But at the same time, it is also a new methodology for the optimization of heterogeneous systems. First, gem5-X is equipped in-simulator with the gperf profiler, which allows to identify application bottlenecks. Once bottlenecks have been identified, gem5-X allows evaluate the potential benefits of advanced architectural extensions such as in-cache computing and 3D stacked High Bandwidth Memory. The performance results of our tuned gem5-X models have been validated against an ARMv8 JUNO board, obtaining an error below 4% when comparing the execution time of the simulator with the real one on the JUNO board. Click here full list of publications and documentation related to gem5-X. |

Usage of gem5-X

gem5-X is the result of our goal to build a framework that enables architectural exploration of current state-of-the-art processors, such as ARMv8 in-order and Out-of-Order architectures. One of the main achievements of gem5-X is that it provides a full working environment around the gem5 simulator, together with a set of models validated against real hardware, as well as enhancements that enable easier and faster development.

The primary intended users of gem5-X are computer architects that want to test architectural extensions on a full system which comprises an operating system (i.e., what in gem5 is named full-system mode) both from academia and industry. We provide researchers with a working and validated environment and setup, to ease the steep learning curve of gem5, providing them with a working out-of-the-box starting point for their experiments. The gem5-X framework is an open-source project, and its main authors would really like to get the computer architecture community engaged and contributing to the project. We believe that having a simulator that allows testing novel architectural extensions from the application level perspective provides a lot of value to the community and bridges the gap between the real application requirements and constraints and the architecture.

Indeed, we provide as separate repositories (still part of the gem5-X github organization) specialized environments including architectural extension. These includes Analog In-Memory Cores (AIMCs), wireless in-package links and tightly-coupled systolic arrays.

Sincerely,

The gem5-X Project Team

Downloading and using gem5-X

Gem5-X is available open-source on Github. You can find here all details on how to install it and use it:

Click here to download gem5-X

Technical Manual

The gem5-X technical manual (August, 2021) is available here:

gem5-X Technical Manual ver. 2Please note that each repository contains a tailored technical manual, which includes dedicated sections covering the implemented architectural extensions.

We are constantly looking out for your feedback and comments in our strive to improve gem5-X. Please send your emails to gem5-x@listes.epfl.ch. You must subscribe to this mailing list in order to be able to communicate with us and also receive notifications about new releases and updates on new patches, bugs etc. Notifications will be kept as limited and as brief as possible and THERE WILL BE NO SPAMMING of your mailbox. In addition, this mailing list will serve as a forum where you can interact with other users of gem5-X.To subscribe, please send an email to gem5-x-subscribe@listes.epfl.ch and follow the instructions in the automatic reply.

For more information about how to (un)subscribe to this mailing list, please read this.

Videos

Related Publications

| Towards Accurate RISC-V Full System Simulation via Component-level Calibration | |||||

| Karan Pathak, Joshua Klein, Giovanni Ansaloni, Said Hamdioui, Georgi Gaydadjiev, Marina Zapater, David Atienza | |||||

| 2025-06-04 | ACM Transactions on Embedded Computing Systems |  |  |  | |

| Gem5-AcceSys: Enabling System-Level Exploration of Standard Interconnects for Novel Accelerators | |||||

| Liu, Qunyou; Zapater, Marina; Atienza, David | |||||

| 2025 | 62nd Design automation conference |  | |||

| Gem5-X : A Many-Core Heterogeneous Simulation Platform for Architectural Exploration and Optimization | |||||

| Qureshi, Yasir Mahmood; Simon, William Andrew; Zapater Sancho, Marina; Olcoz, Katzalin; Atienza Alonso, David | |||||

| 2021 | ACM Transactions on Architecture and Code Optimization (TACO) |  |  |  | |

| Gem5-X: A Gem5-Based System Level Simulation Framework to Optimize Many-Core Platforms | |||||

| Qureshi, Yasir Mahmood; Simon, William Andrew; Zapater Sancho, Marina; Olcoz, Katzalin; Atienza Alonso, David | |||||

| 2019-04-29 | Proceedings of the 27th High Performance Computing Symposium (HPC 2019) |  |  | ||